PACKET ARCHITECTS AB

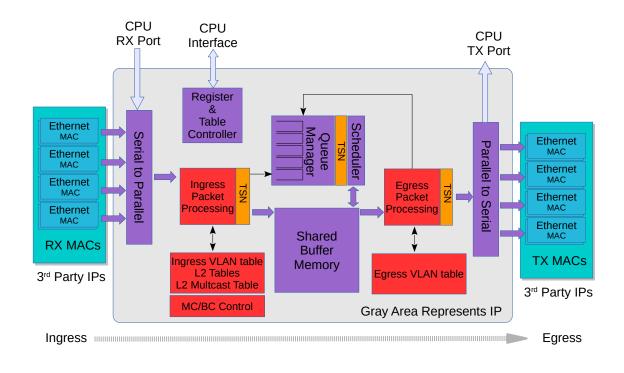

# Ethernet Switch TSN 7x1G + 2x3G User Guide

Core Revision unknown Datasheet Revision unknown March 29, 2024©Packet Architects AB.

# Contents

| 1 | <b>Over</b><br>1.1<br>1.2         | Feature Ov                                                                 | verview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <b>15</b><br>16<br>18                                                                                                                                                                                                                          |

|---|-----------------------------------|----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2 | <b>Pack</b><br>2.1                | et Decoder<br>Decoding                                                     | r<br>Sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <b>21</b><br>21                                                                                                                                                                                                                                |

| 3 | <b>Pack</b><br>3.1<br>3.2         |                                                                            | i <b>ng</b><br>cket Processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <b>27</b><br>27<br>29                                                                                                                                                                                                                          |

| 4 | <b>Later</b><br>4.1<br>4.2        |                                                                            | <b>ter</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <b>31</b><br>31<br>31                                                                                                                                                                                                                          |

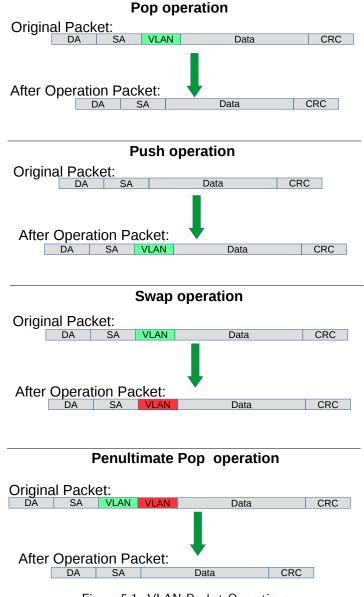

| 5 | VLAI<br>5.1<br>5.2<br>5.3         | 5.1.1<br>5.1.2<br>VLAN mer                                                 | ng<br>tt of Ingress VID .<br>VID Assignment from Packet Fields .<br>Force Ingress VID from Ingress Configurable ACL .<br>mbership .<br>erations .<br>Default VLAN Header .<br>Source Port VLAN Operation .<br>Operation Based On Incoming Packets Number of VLANs .<br>Configurable ACL VLAN Swap Operation .<br>VLAN Table Operation .<br>VLAN Table Operation Based On the Packets Number of VLANs .<br>Egress Port VLAN Operation .<br>Egress Port VLAN Operation .<br>Egress Vlan Translation .<br>Priority Tagged Packets .<br>VLAN Operation Order .<br>VLAN Operation Examples .<br>VLAN Reassembly . | <ul> <li>33</li> <li>33</li> <li>34</li> <li>34</li> <li>34</li> <li>35</li> <li>36</li> <li>37</li> <li>38</li> </ul> |

| 6 | <b>Switc</b><br>6.1<br>6.2<br>6.3 | L2 Destina<br>Software In<br>L2 Action<br>6.3.1<br>6.3.2<br>6.3.3<br>6.3.4 | ation Lookup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <ul> <li>41</li> <li>41</li> <li>42</li> <li>42</li> <li>43</li> <li>43</li> <li>43</li> <li>43</li> <li>43</li> <li>45</li> </ul>                                                                                                             |

|   | 7.1<br>7.2                        | Input Mirr                                                                 | oring                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 45<br>45<br>46                                                                                                                                                                                                                                 |

| 8  | RSPAN - Remote Switch Port Analyzer 47 |                                                                         |            |  |  |

|----|----------------------------------------|-------------------------------------------------------------------------|------------|--|--|

|    | 8.1                                    |                                                                         | 47         |  |  |

|    | 8.2<br>8.3                             |                                                                         | 47<br>48   |  |  |

|    | 0.5                                    |                                                                         | 40         |  |  |

| 9  | Link Aggregation 49                    |                                                                         |            |  |  |

|    |                                        | 9.0.1 One-to-one Port Mapping                                           | 49         |  |  |

|    | 9.1                                    | Example                                                                 | 49         |  |  |

|    | 9.2                                    | Hash Calculation                                                        | 51         |  |  |

| 10 | Class                                  | ification                                                               | 53         |  |  |

| 10 |                                        |                                                                         | 53         |  |  |

|    | 10.2                                   |                                                                         | 53         |  |  |

|    |                                        | 0 0                                                                     | 54         |  |  |

|    |                                        | 10.2.2 Example Of Selecting Fields For Configurable Ingress ACL Table 0 | 58         |  |  |

|    |                                        | 10.2.3 Example Of Selecting Fields For Configurable Ingress ACL Table 1 | 62         |  |  |

|    |                                        |                                                                         | 64         |  |  |

|    |                                        |                                                                         | 64         |  |  |

|    | 10.3                                   |                                                                         | 64         |  |  |

|    |                                        |                                                                         | 64         |  |  |

|    |                                        | 10.3.2 Default Port ACL action                                          | 65         |  |  |

| 11 | VLA                                    | N and Packet Type Filtering                                             | 67         |  |  |

| 12 | Attac                                  | ck Prevention                                                           | 69         |  |  |

|    |                                        |                                                                         |            |  |  |

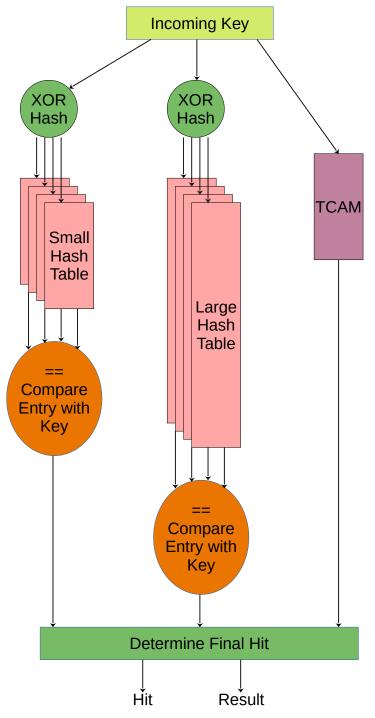

| 13 | Hash                                   |                                                                         | 71         |  |  |

|    | 13.1                                   | <b>6</b>                                                                | 71         |  |  |

|    |                                        |                                                                         | 71<br>72   |  |  |

|    |                                        |                                                                         | 76         |  |  |

|    |                                        |                                                                         | 83         |  |  |

|    |                                        |                                                                         |            |  |  |

| 14 |                                        |                                                                         | 87         |  |  |

|    | 14.1                                   |                                                                         | 87         |  |  |

|    |                                        | 0                                                                       | 87<br>88   |  |  |

|    |                                        | 14.1.2 Ingress Configurable ACL                                         | 00         |  |  |

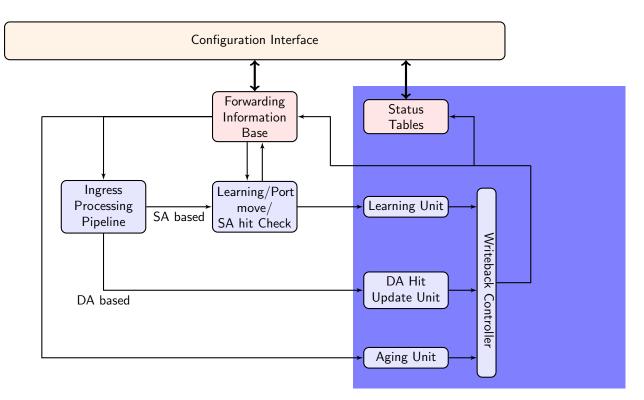

| 15 | Learn                                  | ing and Aging                                                           | 91         |  |  |

|    |                                        |                                                                         | 91         |  |  |

|    |                                        |                                                                         | 91         |  |  |

|    |                                        |                                                                         | 92         |  |  |

|    |                                        |                                                                         | 93         |  |  |

|    | 15.2                                   | 0 0 0                                                                   | 93         |  |  |

|    |                                        | 5                                                                       | 93<br>94   |  |  |

|    |                                        | 0 1                                                                     | 94<br>95   |  |  |

|    |                                        |                                                                         | 95<br>95   |  |  |

|    | 15.3                                   |                                                                         | 95         |  |  |

|    |                                        |                                                                         | 95         |  |  |

|    |                                        |                                                                         | 96         |  |  |

|    | _                                      |                                                                         | <b>~</b> - |  |  |

| 16 |                                        | 0                                                                       | 97         |  |  |

|    | 16.1<br>16.2                           |                                                                         | 97<br>97   |  |  |

|    | 16.2<br>16.3                           |                                                                         | 97<br>98   |  |  |

|    | 10.3                                   |                                                                         | 90         |  |  |

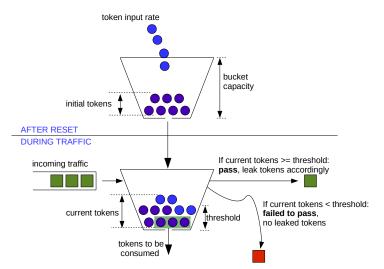

| 17 | Toke                                   | n Bucket                                                                | 99         |  |  |

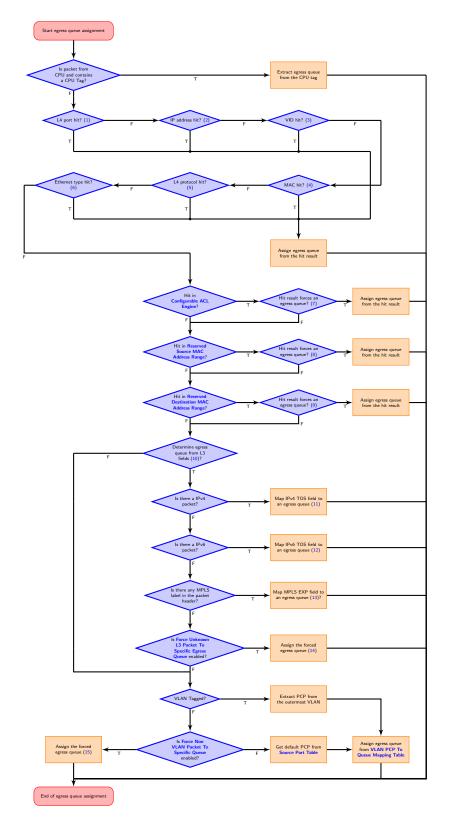

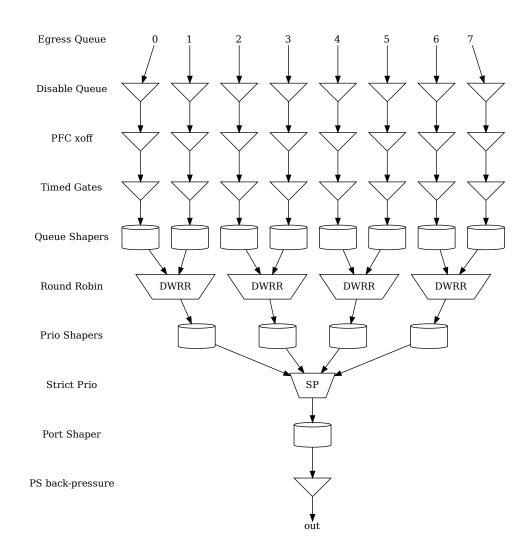

| 18        | Egres | ss Queues and Scheduling                                         | 101 |

|-----------|-------|------------------------------------------------------------------|-----|

|           | 18.1  | Determine Egress Queue                                           | 101 |

|           | 18.2  | Determine a packets outgoing QoS headers PCP, DEI and TOS fields | 103 |

|           |       | 18.2.1 Remap Egress Queue to Packet Headers                      | 103 |

|           | 18.3  | Priority Mapping                                                 | 104 |

|           | 18.4  | Timed Gates For Egress Queues                                    | 104 |

|           |       | 18.4.1 Initialization                                            | 104 |

|           |       | 18.4.2 Admin Configurations                                      | 104 |

|           |       | 18.4.3 Runtime Reconfiguration                                   | 106 |

|           |       | 18.4.4 Impact of Output Disable                                  | 106 |

|           | 18.5  | Shapers                                                          | 106 |

|           |       | 18.5.1 Queue Shaper                                              | 106 |

|           |       | 18.5.2 Prio Shaper                                               | 106 |

|           | 18.6  | Scheduling                                                       | 108 |

|           | 18.7  | DWRR Scheduler                                                   | 108 |

|           | 18.8  | Queue Management                                                 | 108 |

|           | 18.9  | How To Make Sure A Port Is Empty                                 | 109 |

|           |       |                                                                  |     |

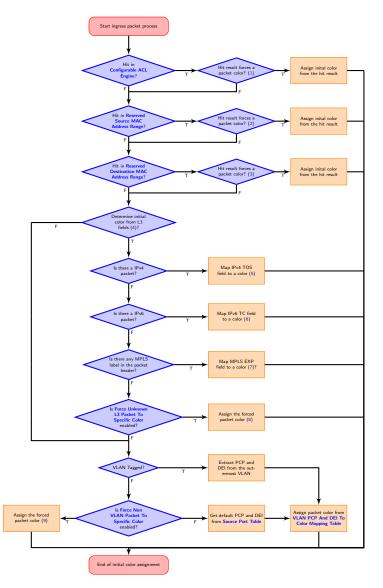

| 19        | Pack  | et Coloring                                                      | 111 |

|           | 19.1  | Ingress Packet Initial Coloring                                  | 111 |

|           | 19.2  | Remap Packet Color to Packet Headers                             | 112 |

| •••       |       |                                                                  | 446 |

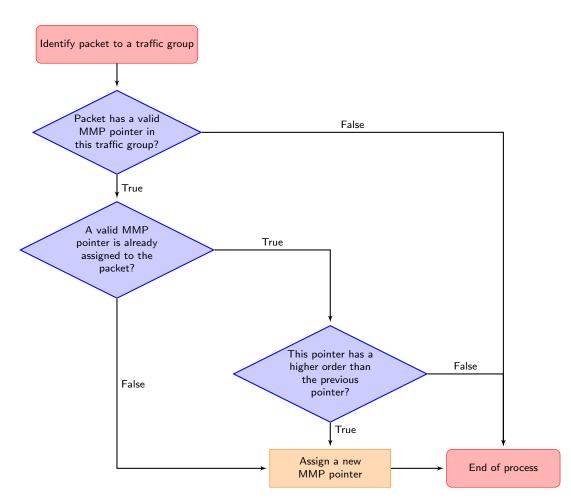

| 20        |       | ission Control                                                   | 115 |

|           | 20.1  | Ingress Admission Control                                        | 115 |

|           | 20.0  | 20.1.1 Traffic Groups                                            | 115 |

|           | 20.2  | Meter-Marker-Policer                                             | 116 |

| 21        | Per-S | Stream Filtering and Policing                                    | 119 |

|           | 21.1  | Stream Filter                                                    | 119 |

|           | 21.1  | 21.1.1 Max SDU Filter                                            | 119 |

|           | 21.2  | Stream Gate / Ingress Transmission Gate                          | 120 |

|           |       | 21.2.1 Configuration and Constraints                             | 120 |

|           | 21.3  | Flow Meter                                                       | 120 |

|           | 21.4  | Stream Blocking                                                  | 121 |

|           | 21.5  | Statistics                                                       | 121 |

|           |       |                                                                  |     |

| 22        | Fram  | e Replication and Elimination for Reliability                    | 123 |

|           | 22.1  | Enabling FRER                                                    | 123 |

|           | 22.2  | Generation Mode                                                  | 123 |

|           | 22.3  | Recovery Mode                                                    | 124 |

|           | 22.4  | Internal State                                                   | 124 |

|           | 22.5  | Redundancy Tag                                                   | 124 |

|           | 22.6  | Statistics                                                       | 125 |

| •••       |       |                                                                  | 107 |

| 23        | Tick  |                                                                  | 127 |

|           | 23.1  |                                                                  | 127 |

|           | 23.2  | PTP Ticks                                                        | 127 |

| 24        | Multi | icast Broadcast Storm Control                                    | 129 |

| 24        | 24.1  |                                                                  | 129 |

|           | 24.1  | Rate Configuration                                               | 129 |

|           | 27.2  |                                                                  | 100 |

| 25        | Ingre | ss Rate Control                                                  | 133 |

| -         | 25.1  | Determine ingress queue                                          | 133 |

|           | 25.2  | Inspected Traffic                                                | 133 |

|           | 25.3  | Configuration                                                    | 133 |

|           |       |                                                                  |     |

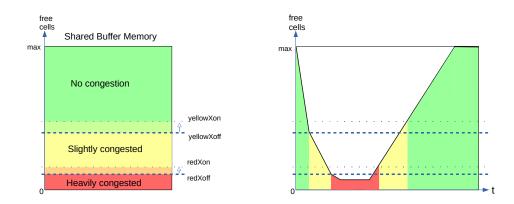

| <b>26</b> | Egres | ss Resource Manager                                              | 135 |

|     | 26.1   | Yellow Zone                                                   |

|-----|--------|---------------------------------------------------------------|

|     | 26.2   | Red Zone                                                      |

|     | 26.3   | Green Zone                                                    |

|     | 26.4   | Configuration Example                                         |

|     | 26.5   | Restrictions                                                  |

|     |        |                                                               |

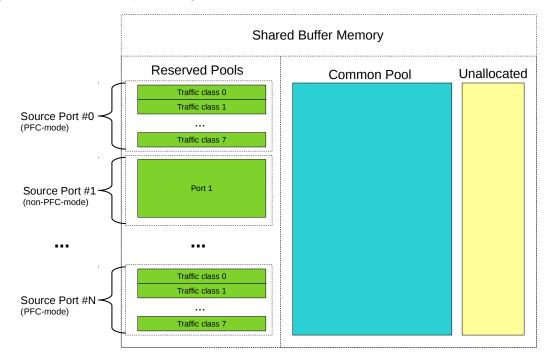

| 27  | Flow   | Control 139                                                   |

|     | 27.1   | Pausing                                                       |

|     | 27.2   | Tail-Drop                                                     |

|     |        | 27.2.1 Tail-drop as police for Pausing                        |

|     | 27.3   | Buffer partitioning                                           |

|     | 21.5   | 27.3.1 Reserves                                               |

|     | 07.4   |                                                               |

|     | 27.4   |                                                               |

|     | 27.5   | PFC-mode                                                      |

|     |        | 27.5.1 Pausing Thresholds                                     |

|     |        | 27.5.2         Tail-drop Thresholds         142               |

|     | 27.6   | Enabling Tail-Drop                                            |

|     | 27.7   | Enabling Pausing                                              |

|     | 27.8   | Dropped packets                                               |

|     | 27.9   | Reconfiguration                                               |

|     | 27.10  | Debug Features                                                |

|     |        |                                                               |

| 28  | Egres  | s Port Shaper 145                                             |

|     | •      |                                                               |

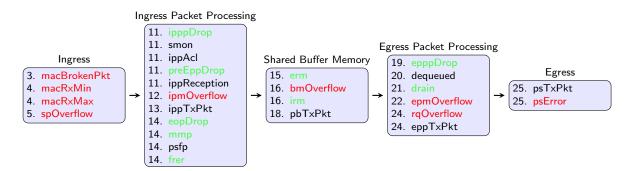

| 29  | Statis | tics 147                                                      |

|     | 29.1   | Packet Processing Pipeline Drops                              |

|     | 29.2   | ACL Statistics                                                |

|     | 29.3   | SMON Statistics                                               |

|     | 29.4   | Ingress Port Receive Statistics                               |

|     | 29.5   | Packet Datapath Statistics                                    |

|     | 29.6   | Miscellaneous Statistics                                      |

|     | 29.7   | Debug Statistics                                              |

|     | 29.1   |                                                               |

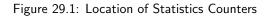

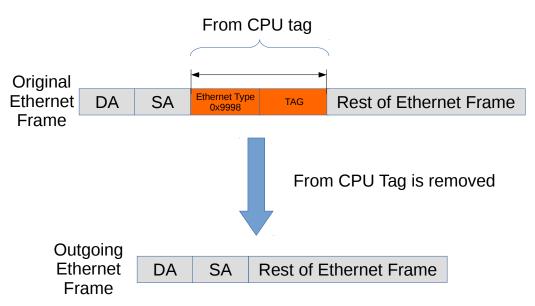

| 30  | Packe  | ts To And From The CPU 151                                    |

| ••• | 30.1   | Packets From the CPU                                          |

|     | 00.1   | 30.1.1 Identify the From CPU Tag                              |

|     |        | 30.1.2 From CPU Header and Packet Modification and Operations |

|     | 30.2   | Packets To the CPU                                            |

|     | 30.2   |                                                               |

|     |        |                                                               |

|     |        | 30.2.2 Reason Code Operations                                 |

| 21  | Coro   | Interface Description 157                                     |

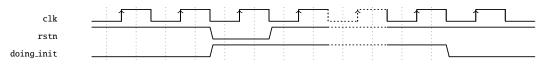

| 31  | 31.1   | -                                                             |

|     | 51.1   |                                                               |

|     | 21.0   | 31.1.1 Assert Reset                                           |

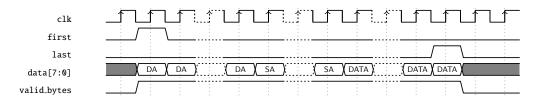

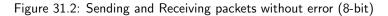

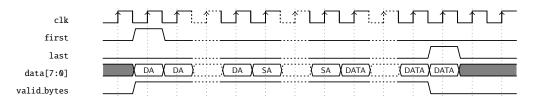

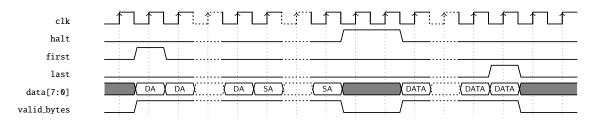

|     | 31.2   | Packet Interface                                              |

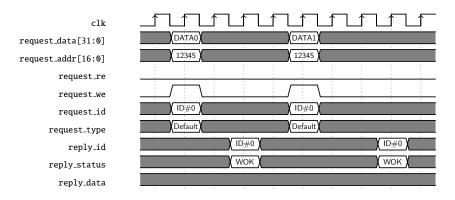

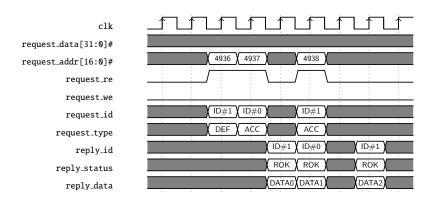

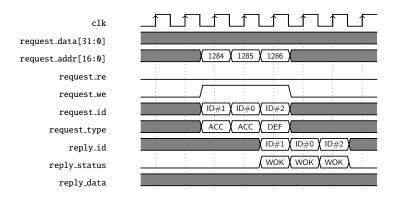

|     | 31.3   | Configuration Interface                                       |

|     | 31.4   | Pause Interfaces                                              |

|     |        | 31.4.1 PFC Status                                             |

|     |        | 31.4.2 External Pause                                         |

|     | 31.5   | Debug Read Interface                                          |

|     | 31.6   | Debug Write Interface                                         |

|     |        |                                                               |

| 32  | Confi  | guration Interface 169                                        |

|     | 32.1   | Request Types                                                 |

|     | 32.2   | Reply Types                                                   |

|     | 32.3   | Transaction Identifier                                        |

|     | 52.5   |                                                               |

|     | 32.4   | Atomic Wide Access - Accumulator Access                       |

| 33  | Imple | mentation        |                                               | 173        |

|-----|-------|------------------|-----------------------------------------------|------------|

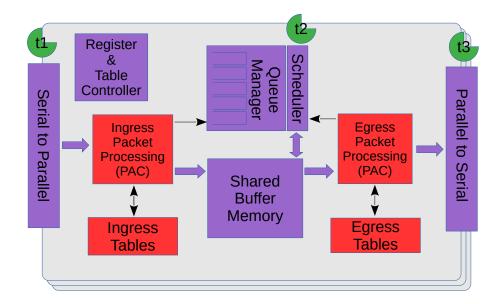

|     | 33.1  | Floorplann       | ing                                           | 173        |

|     |       | 33.1.1           | Pipelining                                    | 173        |

|     |       | 33.1.2           | Configuration and debug                       | 174        |

|     |       | 33.1.3           | IPP and EPP Structure                         | 174        |

|     | 33.2  | Memory w         | rappers                                       | 174        |

|     | 33.3  | Dual porte       | d memories                                    | 175        |

|     | 33.4  | Memory til       | ming                                          | 176        |

|     | 33.5  | Lint set up      | )                                             | 176        |

|     |       | 33.5.1           | Waivers                                       | 176        |

| ~ ~ |       |                  |                                               |            |

| 34  |       | ters and Ta      |                                               | 177        |

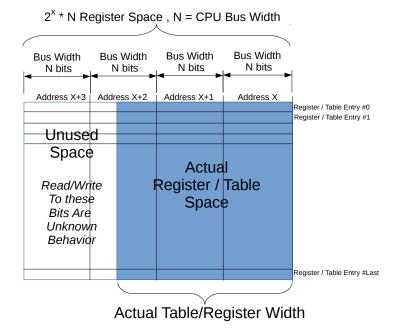

|     | 34.1  |                  | pace For Tables and Registers                 | 184        |

|     | 34.2  |                  | r                                             | 185        |

|     | 34.3  |                  | anks                                          | 185        |

|     | 34.4  | -                | Ind Tables in Alphabetical Order              | 192        |

|     | 34.5  |                  |                                               | 198        |

|     |       | 34.5.1           | ERM Red Configuration                         | 198        |

|     |       | 34.5.2           | ERM Yellow Configuration                      | 199        |

|     |       | 34.5.3           | Egress Resource Manager Pointer               | 200        |

|     | 24.6  | 34.5.4           | Resource Limiter Set                          | 200        |

|     | 34.6  |                  | nation                                        | 201        |

|     | 247   | 34.6.1           | Core Version                                  | 201        |

|     | 34.7  |                  | Sket Processing   Sket Processing             | 201        |

|     |       | 34.7.1<br>34.7.2 | Color Remap From Egress Port                  | 201<br>202 |

|     |       | 34.7.3           | Color Remap From Ingress Admission Control    | 202        |

|     |       | 34.7.4           | Disable CPU tag on CPU Port                   | 202        |

|     |       | 34.7.5           | Egress Ethernet Type for VLAN tag             | 203        |

|     |       | 34.7.6           | Egress Multiple Spanning Tree State           | 203        |

|     |       | 34.7.7           | Egress Port Configuration                     | -          |

|     |       | 34.7.8           | Egress Port VID Operation                     |            |

|     |       | 34.7.9           | Egress Queue To PCP And CFI/DEI Mapping Table |            |

|     |       | 34.7.10          | Egress RSPAN Configuration                    |            |

|     |       | 34.7.11          | Egress VLAN Translation Large Table           |            |

|     |       | 34.7.12          | Egress VLAN Translation Search Mask           |            |

|     |       | 34.7.13          | Egress VLAN Translation Selection             |            |

|     |       | 34.7.14          | Egress VLAN Translation Small Table           |            |

|     |       | 34.7.15          | Egress VLAN Translation TCAM                  |            |

|     |       | 34.7.16          | Egress VLAN Translation TCAM Answer           |            |

|     |       | 34.7.17          | Output Mirroring Table                        |            |

|     | 34.8  |                  | rol                                           |            |

|     |       | 34.8.1           | FFA Used PFC                                  |            |

|     |       | 34.8.2           | FFA Used non-PFC                              |            |

|     |       | 34.8.3           | PFC Dec Counters for ingress ports 0 to 8     |            |

|     |       | 34.8.4           | PFC Inc Counters for ingress ports 0 to 8     |            |

|     |       | 34.8.5           | Port FFA Used                                 |            |

|     |       | 34.8.6           | Port Pause Settings                           |            |

|     |       | 34.8.7           | Port Reserved                                 |            |

|     |       | 34.8.8           | Port Tail-Drop FFA Threshold                  |            |

|     |       | 34.8.9           | Port Tail-Drop Settings                       |            |

|     |       | 34.8.10          | Port Used                                     |            |

|     |       | 34.8.11          | Port Xoff FFA Threshold                       | 216        |

|     |       | 34.8.12          | Port Xon FFA Threshold                        | 216        |

|     |       | 34.8.13          | Port/TC Reserved                              | 217        |

|     |       | 34.8.14          | Port/TC Tail-Drop Total Threshold             | 217        |

|     |       | 34.8.15          | Port/TC Xoff Total Threshold                  |            |

|     |       |                  |                                               |            |

|       | 34.8.16    | Port/TC Xon Total Threshold                               | 218                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------|------------|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | 34.8.17    | TC FFA Used                                               | 218                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|       | 34.8.18    | TC Tail-Drop FFA Threshold                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|       | 34.8.19    | TC Xoff FFA Threshold                                     | 219                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|       | 34.8.20    | TC Xon FFA Threshold                                      | 220                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|       | 34.8.21    | Tail-Drop FFA Threshold                                   | 220                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|       | 34.8.22    | Xoff FFA Threshold                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|       | 34.8.23    | Xon FFA Threshold                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 34.9  | Global Co  | nfiguration                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|       | 34.9.1     | CPU Port                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|       | 34.9.2     | Core Tick Configuration                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |